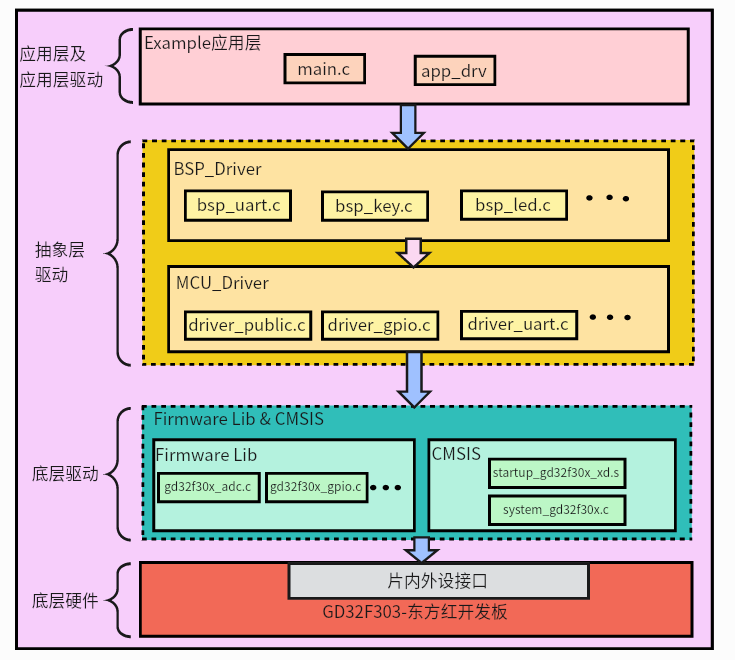

大家一定遇到过上电或者复位时外部的MOS电路或者芯片使能信号意外开启,至此有经验的工程师就会经常关心一个问题,MCU复位时GPIO是什么状态?什么电路需要外部加上下拉?

首先MCU上电过程到POR复位前,数字电路逻辑还没复位,GPIO处于高阻状态,NMOS、PMOS、上下拉电阻都处于关闭状态,此时GPIO处于高阻状态。

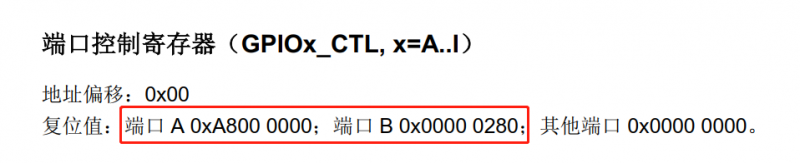

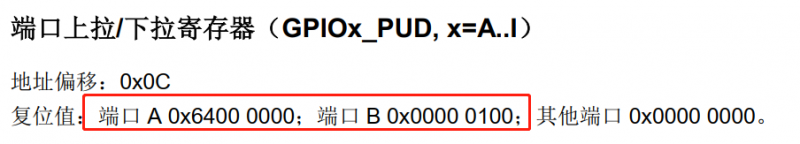

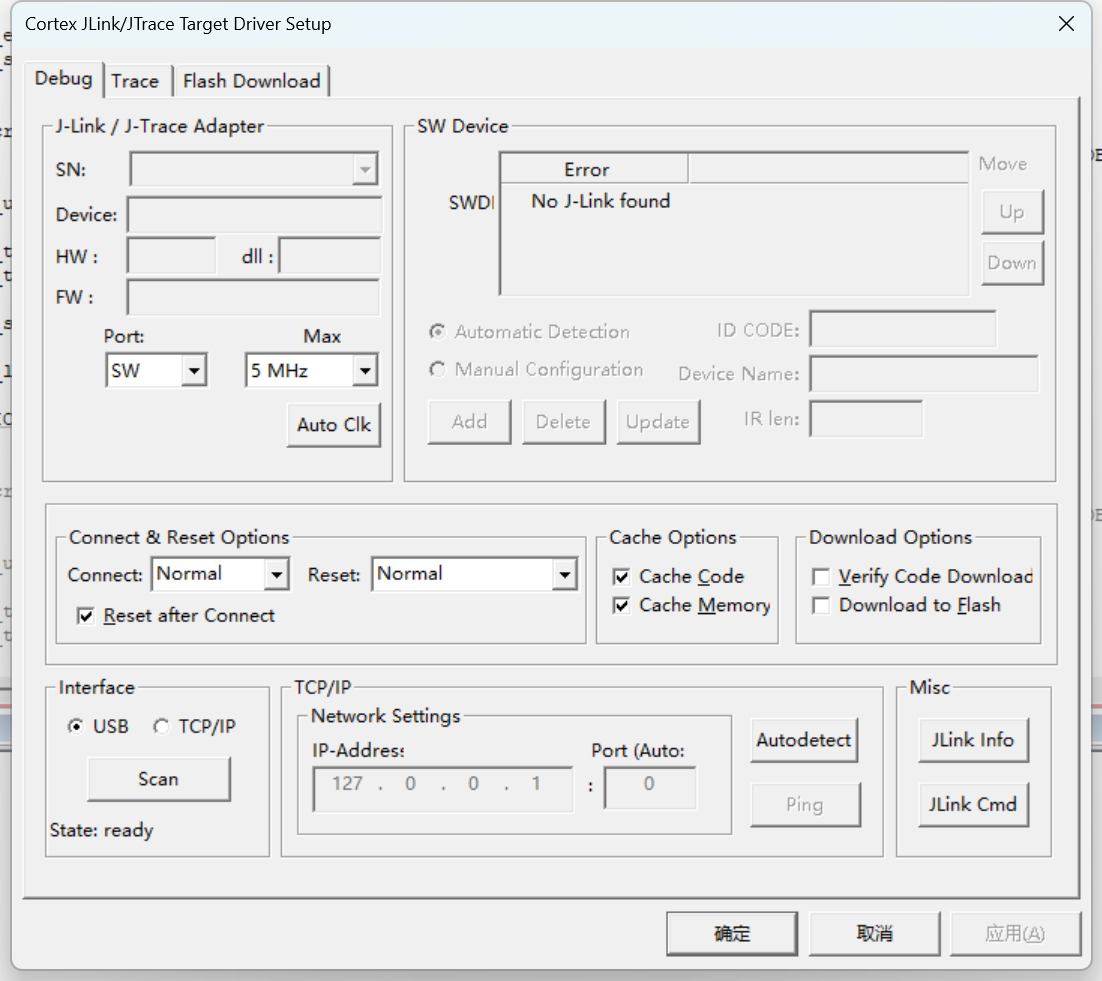

当MCU POR复位后,复位引脚拉高,寄存器全部加载复位值,此时IO口状态我们可以从GPIO寄存器中看到:

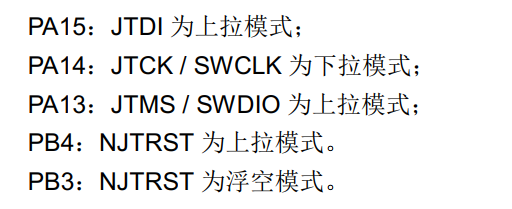

可以看到JTAG和SWD相关的引脚默认状态都是复用模式,且其中部分有配置默认的内部上下拉:

所以当MCU复位后,GPIO初始化前一些特殊GPIO是会有内部上下拉或者输出状态的,我们需要根据电路电平要求来合理选用GPIO,避免复位时IO口出现误输出。

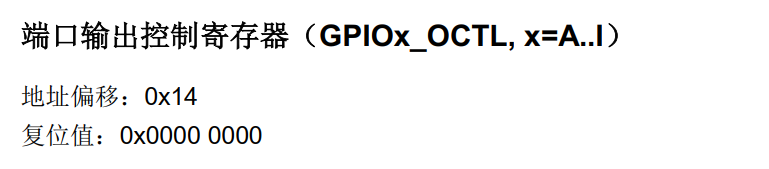

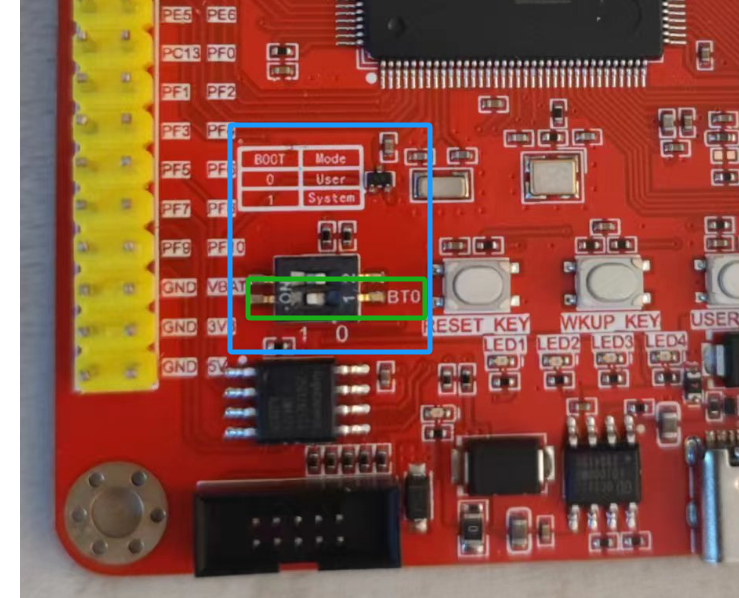

程序启动后执行初始化时会配置想要的GPIO模式和状态,此时一样也可能出现误输出,我们来看下GPIO输出寄存器默认值:

因为复位值是全0,所以如果一个希望默认为高的IO先初始化GPIO为输出模式再配置默认状态,那么GPIO会先输出低电平再马上拉高,通过示波器会看到复位后MCU IO口出现一个低电平毛刺,那么合理可靠的配置时序是:

1、先打开GPIO时钟;2、设置GPIO输出高还是低;3、设置GPIO模式;

这样就不会在初始化过程出现毛刺,需要严格遵守。

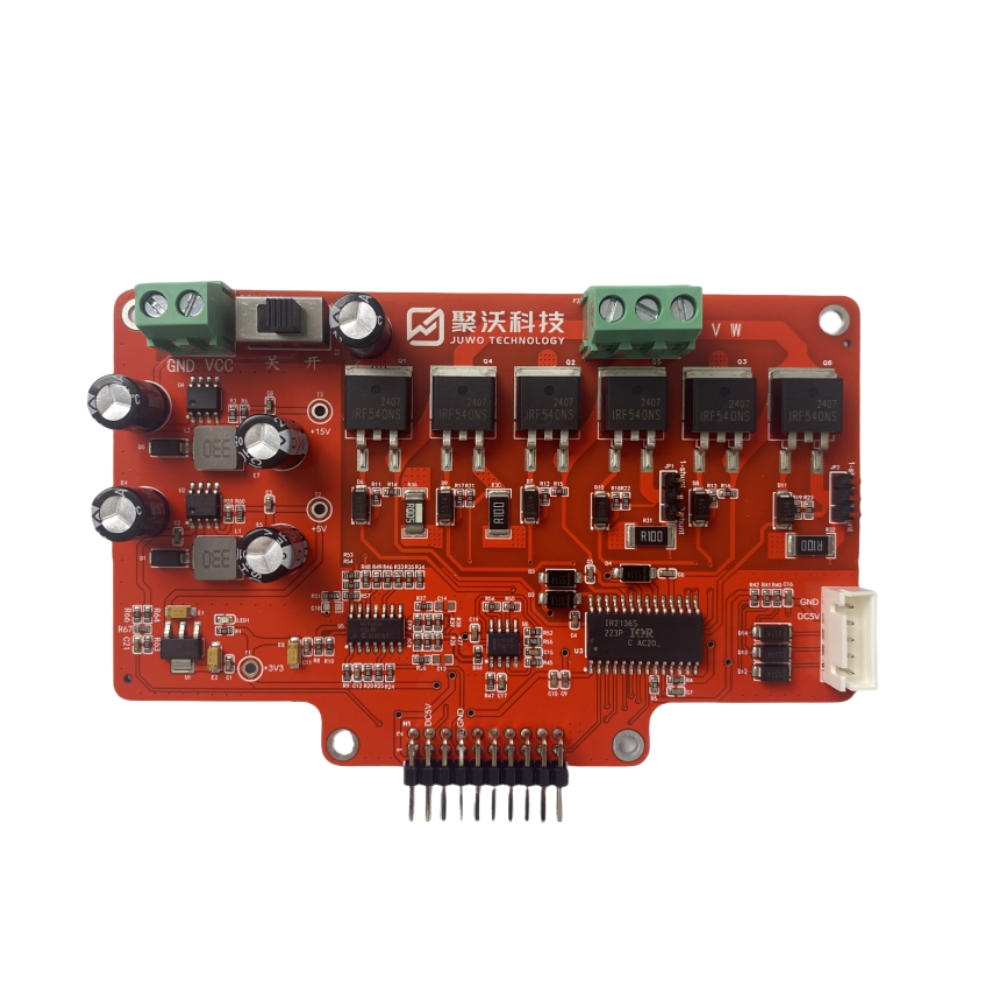

那么我们现在知道了,除去一些特殊IO和软件配置时序我们需要注意,在MCU IO口初始化前其他IO都是高阻状态,那么高阻状态是什么电压?需不需要上下拉,那我们则需要根据外围电路来判断,请关注我们,后续视频我们继续分享。

发表评论 取消回复